Nestas férias da minha segunda inscrição no curso de Electronica e Telecomunicações da Universidade de Aveiro, decidi por em prática os conhecimentos adquiridos em Laboratórios de Sistemas Digitais.

Dos vários projectos que gostava de levar a cabo, decidi pelo projecto do computador de 8 bits do Ben Eater. Ainda no decurso do primeiro semestre deste ano (21/22) pensei em executar o projecto exactamente como ele é proposto pelo o Ben Eater.

Cheguei a comprar os diversos ICs necessários á sua execução, e conclui o modulo de relógio. No entanto, o tempo não me permitiu executar o projecto.

Nas férias entre semestres, passei a outro projecto, e o tempo foi dedicado á construção de um computador com o Z80 baseado no projecto RC2014, cujos PCBs de face simples são fabricados numa CNC 3018. Este projecto foi concluído até ao final da primeira fase (executa o monitor SCM).

Nestas férias pensei voltar ao computador de 8 bits do Ben Eater, só que em vez de o efectuar tal como proposto, decidi efectua-lo em VHDL para ser implementado numa placa de testes RZ-EasyFPGA-2.2, que comprei no Aliexpress.

Uma pesquisa na internet permitiu descobrir que já existem uma serie de projectos que implementam o computador de 8 bits do Ben Eater (ou variações) em VHDL. Dos projectos que encontrei destaco os seguintes:

http://www.jk-quantized.com/blog/2017/10/20/a-vhdl-take-on-ben-eaters-cpu

https://salihujohn.com/portfolio/ben-eater-8-bit-breadboard-computer-on-an-fpga/

https://github.com/XarkLabs/BenEaterVHDL

Após uma breve vista de olhos a estes projectos, decidi efectuar uma implementação que partisse da modelação dos componentes da serie 74 usados.

Além de ser baseado na modelação desses componentes, a implementação que pretendo levar a cabo também vai ter por base os mesmos módulos tal como estão descritos nos esquemas do Ben Eater.

O computador de 8 bits do Ben Eater está bem documentado na seguinte pagina:

https://eater.net/8bit

Pelo que seguirei com detalhe essa documentação.

O computador de 8 bits do Ben Eater está estruturado em 8 modulos principais:

Relógio

Neste momento é simplesmente um clock divider em VHDL

Registos (A, B e instrução)

2022/07/09 – Fase 1 – Implementada e testada.

Apesar de ter sido bem sucedida e o teste na fpga funcionar. Esta fase revelou uns problemas na simulação com portos bidireccionais, quer com o simulador interno do quartus, quer com o modelsim.

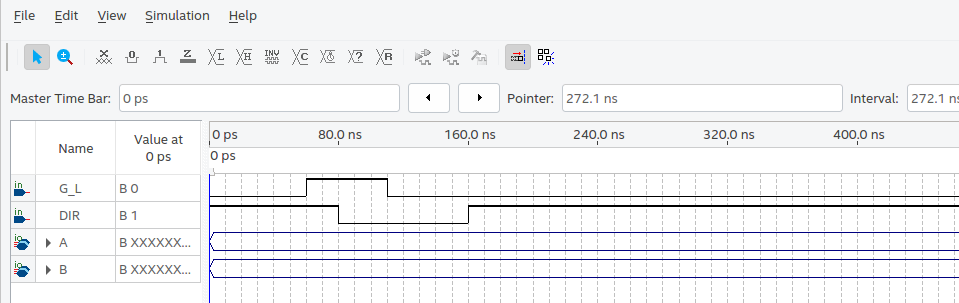

Por exemplo na simulação do IC 74245, inicialmente consegui executar a simulação e obter o resultados previstos. Mais tarde sem ter efectuado qualquer alteração no VHDL do componente a simulação já não estava de acordo com o previsto. Na imagem seguinte estão os estímulos aplicados. De notar que A e B são bidirecionais.

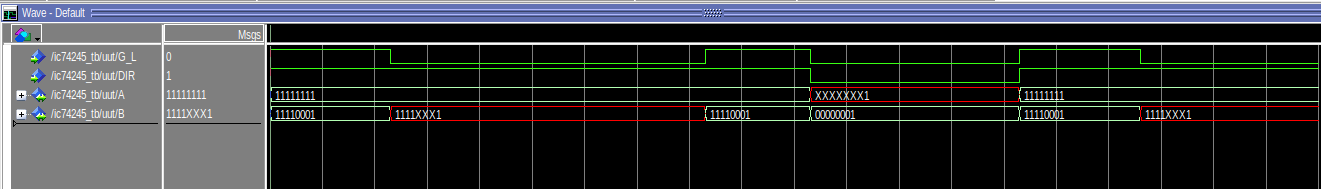

Na imagem seguinte está o resultado das ultimas simulações efectuadas. O A e B tem XXXXXXXX, em vez de terem o resultado previsto.

O mesmo problema aconteceu com a simulação do gp_register (baseado nos IC’s 74245 e 74173). Não consigo entender porque é que as simulações de componentes bidireccionais deixaram de funcionar.

Na simulação do modelsim os resultados não foram muito melhores.

As zonas a vermelho indicam o conflito nos bits que deviam ter sido transferidos.

Nota de 16/07/2022 : após algum tempo, descobri que é possivel corrigir este problema, ou seja voltar a ter simulações correctas, quando usamos a opçao:

Project > Clean Project

Parece que numa das minhas experiências com o IC74245, devo ter alterado incorrectamente e um ficheiro gerado com a versão incorrecta numa mais foi substituído. Com o Clean Projecto o ficheiro foi reconstruido e a simulação ficou correcta.

Gostava de mais tarde integrar um teclado para inserir valores para fazer mais testes.

Unidade Lógica e Aritmética (e registo de Flags)

IC ‘s 74173, 74245, 74283, 7486, 7402, 7408

notas:

O IC 74283 não está implementado conforme o datasheet com o fast carry, mas sim uma versão mais simples. Se não funcionar por causa dos atrasos terei que modelar exactamente conforme o datasheet.

O IC 7486 são 4 portas xor de 2 entradas. Em VHDL não faria muito sentido estar a modelar este IC, mas de modo a aderir ao design do Ben Eater o IC é modelado e usado. O mesmo acontece com o 7402 e 7408.

2022/07/10 – Fase 2 – Inicialmente os bits que saiam para o bus estavam com a ordem trocada, e o ZF estava mal. Consegui resolver a ordem dos bits, mas as flags tem qualquer coisa que não percebi.

Independentemente das flags estarem bem calculadas, ou não, vou avançar. Mais tarde reavaliarei este problema e tentarei resolver.

Memória RAM

Este módulo está dividido em duas partes, cada uma com o seu esquema.

Memory address register (MAR)

IC’s 74157, 74173

RAM module

IC’s 7400, 7404, 74157, 74189, 74245

Ainda não percebi bem o seu funcionamento pois os switches deixam portas a flutuar. Apesar de não ter as portas físicas para os diversos switches e botões envolvidos, vou inclui-los na mesma como portos de entrada.

Queria ver se conseguiria adaptar mais tarde um teclado ps/2 de modo a alimentar os valores para alguns dos switches.

O MAR foi implementado (mar.vhd) e testado com sucesso numa simulação VWF.

O RAM module foi também implementado (RAM16b.vhd). Se bem que não seja possível colocar o condensador no sinal de clock, procurei manter o de design o mais próximo do modelo em breadboard.

A síntese indica vários erros.

Warning (13012): Latch IC74189:mem_u24|s_memory~40 has unsafe behavior Warning (13013): Ports D and ENA on the latch are fed by the same signal PROG

Este modulo é composto pelos elementos de memória se

2 ics 74189, memórias de 16 posições de 4 bit, assincronas, com sinais de controlo: “Chip Select” (active low) e Write Enable” e outputs tristate.

3 ics 74157, 4 multiplexers de 2 para 1 , com select partilhado, que se são necessários para fazer a programação no modele em breadboard.

Os dados são guardados, na memoria, em função do sinal PROG, usado como select para origem dos dados a serem armazenados no endereço de memória seleccionado (definido no bus de endereços), e também como select da origem do sinal de “Write enable” para proceder ao registo dos dados disponíveis seja activado.

No acesso de leitura 8 bits (dbus), os dados disponibilizados são os existentes no registo indicado pela linha de endereços, que, em função dos sinais de controlo adequados, os disponibiliza (registo), como inputs de um buffer configurado apenas na direcção de saída para o dbus.

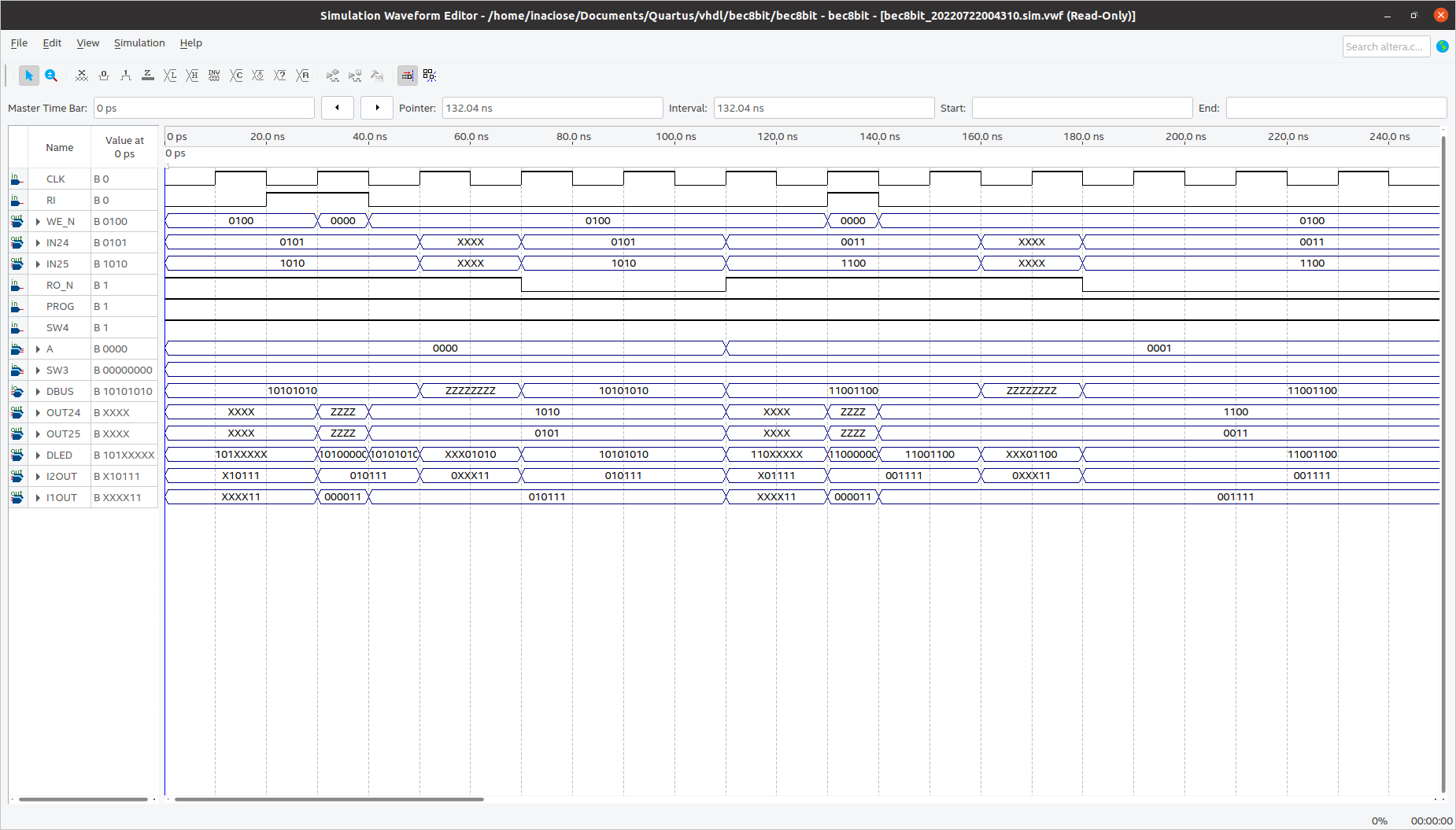

As tentativas de simulação revelaram uns valores inesperados, que ainda não consegui entender, e resolver.

Destaca-se na imagem mais abaixo as seguintes situações:

Entre os 280ns está 00h no bus de dados. Instantes antes, são aplicados os sinais apropriados, para colocar esse valor na posição de memória adequada, entretanto, uns nanos segundos depois deixam-se de injectar o 00h, no bus de dados e este fica em alta impedancia. Aos 390ns é activada a saida do buffer, que supostamente iria apresentar o valor previamente guardado, já que o endereço selecionado é o mesmo, era esperado 00h, mas no entanto o que aparece no bus é E0h.

Como infelizmente não consegui simular correctamente este modulo, não sei se os valores não estão viciados por alguma razão. Como não efectuei nenhum teste prático não faço ideia se está a funcionar correctamente. Mas tudo indica que não.

Contador do programa (PC)

IC’s 74161, 74245

Este modulo foi efectuado (pc.vhd) e testado no simulador.

Registo de Saída

Este modulo foi efectuado (output_register.vhd) e testado na prática com os ficheiros : io_shell5 e topshell5

Lógica de Controlo da CPU

Esta lógica de controlo é implementada no modelo da breadboard recorrendo a tabelas de sinais guardados em ROM.

Inicialmente pensei fazer esta ultima parte como uma maquina de estados, no entanto por ocasião deste momento de escrita decidi que o melhor seria aderir ao modelo mais próximo da breadboard, e implementar recorrendo ás ROMS

Está por fazer, e neste momento o projecto foi suspenso.

Ligar tudo

Depois, se alguma vez completar a a lógica de controlo o passo seguinte será ligar todos os componentes.

Alguns dos vários componentes já tem ficheiros de teste que permitem exemplos para implementar o circuito final em que todos os componentes interagem de forma concertada.

Projecto do quartus disponivel em

https://github.com/inaciose/RZ-easyFPGA-A2.2/tree/main/ben-eater-8bit